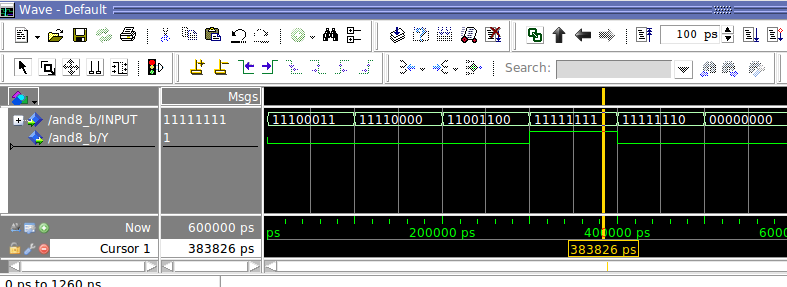

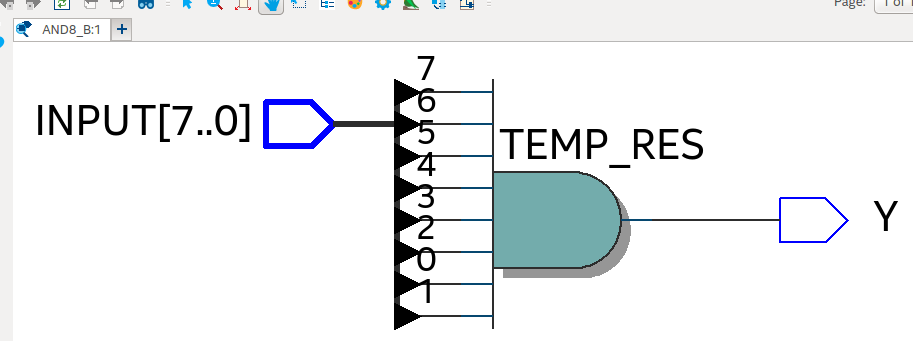

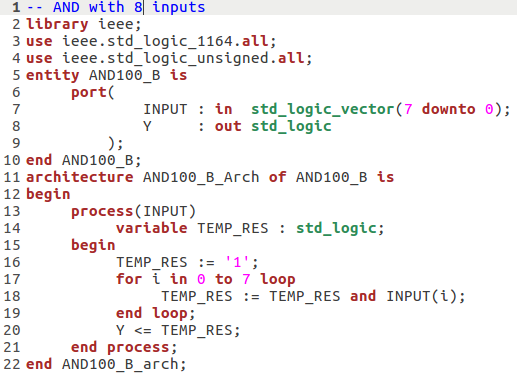

we can duplicate H\W in loop using process, we used loop in process that have one temporary variable for calculations purpose, we first initialized it to '1' otherwise result will stuck at '0' and then we duplicated it using for loop eachtime doing and with the input after loop dont we assign the the result to the output Y note that

when we assign to variable we use the := operator.

when we assign to the signal or outputs(out\inout\buffer) we use the <= operator.

Additional note

1. we build it from 8 gates. instead we can do 100 or 2000 just change the index in the vectors.

2. we have onlt input (as vector) and it must appear in process sensitivity list.

3. variables are are exist inside process only.

4. for loop used to duplicate H\W in process, it also have its own variable i that not need to be declared explicitly we can use it inside the loop scope (till end loop).

Alternative describe of AND with 8 gates using generate statment here.

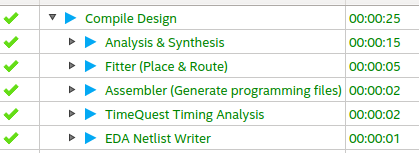

we used it with same exact TCL script we used to simulate the AND8 in the duplication using generate.