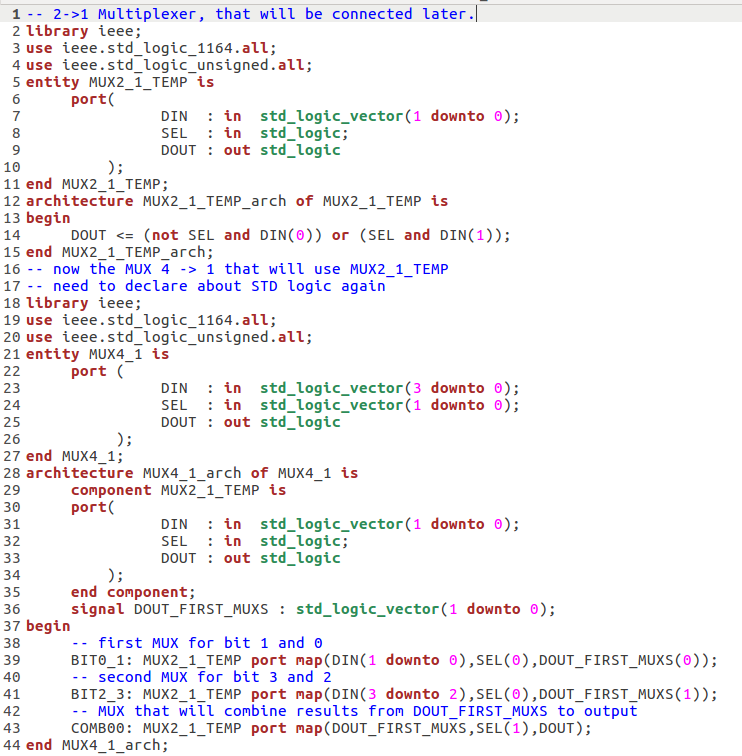

we can discribe H\W by connecting it from small parts as components, lets show simmilar example of mux 4 -> 1 , alternative way of describe we show early here.

syntax

component name of entity is

port sections and other statmetns like in the entity itself

end component;

Notes about using components

1. the entity (and then the arcthiecture) that we want to connect can be in same file or different file, but it need be compolied to the work folder before.

in the waveform we get 'U' as MUX2_TEMP was not discribed.

2. we can have multiple components and all of them need to be defined as component in the architecture declarative area before the begin statment.

3. we may need to use intermidiate signals to connect between the components in the architecture like DOUT_FIRST_MUXS.

4. when using the component Labal is mandatory.

5. when connecting the component we use port map statment and inside the port map we put

- inputs\outputs from port of the entity of the architecture (NOT the compoenent).

- interal signals of the architecture.

6. need to add library ieee; and other use statments before every new entity.

when to use components

1. During design of big projects when there is need to seperate the logic into many components due to its complexity, or when there is large amount of people work on it.

2. for writing Test Bench to test the code.

3. when there is need for logic that cannot pass synthesis but needed exclusivly for simulation.

The wave form act simmilar to previus example of the MUX 4-1 also we use same exact TCL (*.DO) script to show the same exact behaive.