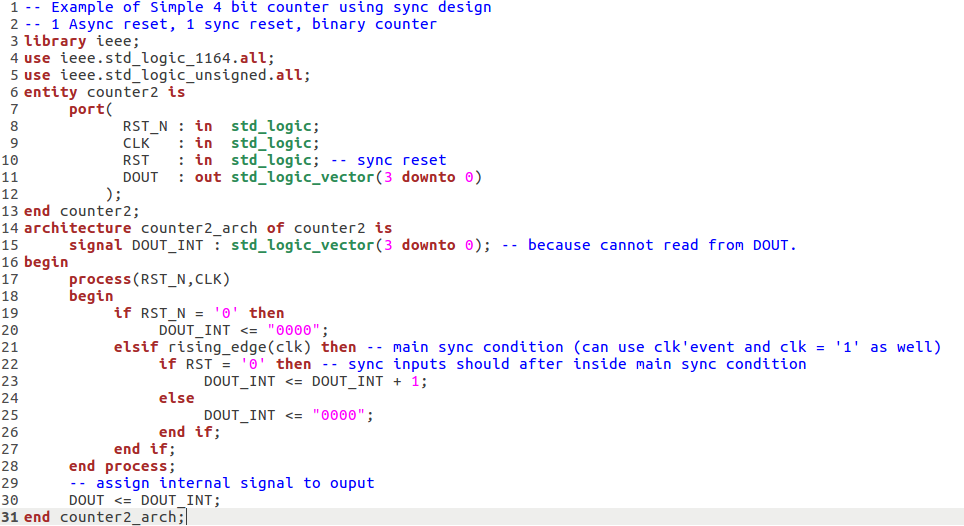

writted in VHDL compiled with Modelsim - adding sync reset

- we have async reset before the main sync condition (rising_edge(clk))

- we can also use clk'event and clk = '1' however because we use std_logic

if can cause problems with simulation of weak values like 'L' and 'H'

while rising_edge(clk) support std_logic data type, also most of the Synthesis tools

Like quartos have direct support for this function. (here tested on 17.1 Lite)

1. open modelsim and ensure you are in the directory where counter1.vhd is

2. write vlib work (if already did you can skip, if u not skip command will not do anything)

3. to compile write vcom counter2

then you will see that modelsim will load your VHDL file and compile it , modelsim will store in work folder

data that is relevant to the compilation

1. write vsim %nameOfEntity% (no .vhd extention)

2. to see the waveforms write add wave * the * mean that it will add all the ports\inputs.

3. force CLK 0 , 1 50 ns -r 100 ns it will make the clock signal (repeated)

4. force RST_N 0 , 1 100 ns will put RST_N to 0 for 100 ns then to '1'.

5. force RST 0 - we want to use sync reset later

6. run 1000 ns will run for 1000 ns

7. force RST 1 set sync reset to 1

8. run 100 ns let it run for 1 cycle to reset the count.

9. force RST 1 set sync reset to 0

10. run 1000 ns continue count again.

note that when sync reset is '1' then counter is reset "0000".