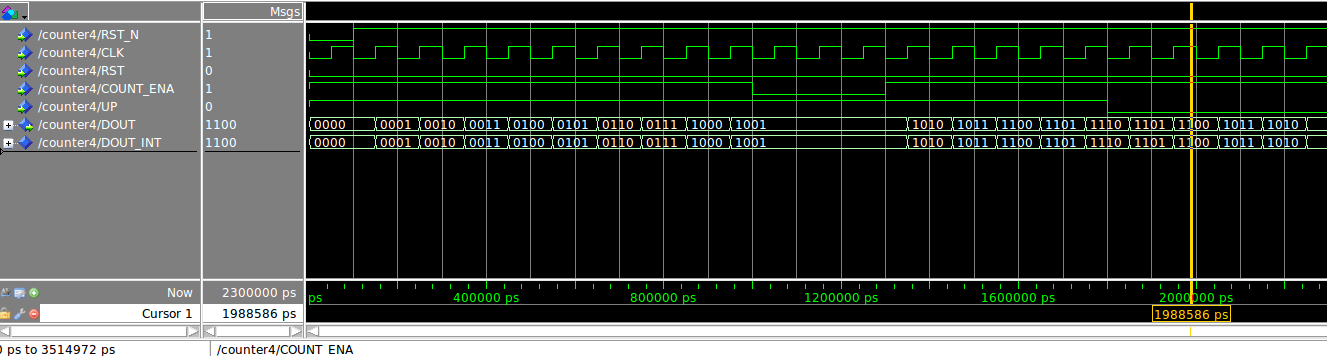

writted in VHDL compiled with Modelsim - 4 bit counter with count enable,sync reset and up\down selection

- we have async reset before the main sync condition (rising_edge(clk))

- we wrep the counting DOUT_INT <= DOUT_INT + 1; with if that will check

if COUNT_ENA is '1' if it not it will not count.

- inadditon we have UP inout that decide of we will count uo or down.

Below are pure Sync Design Example that have combinational Logic and it have Memory (registers) Below counter contain the async inputs before the main synh statement (rising_edge()), it have aswell as sync features like reset,counter anable and direction.

From SM view (State Machine) below are moore SM as the inputs do not change the output directly but via synh condition, as well as any input (like UP) do not trigger the process at all!

as previus to simulation became long and it preffered to use modelsim script (based on TCK\TK)

we can see that when COUNT_ENA is 0 counter stop count.

as well as we can see when UP = 0 count is down.