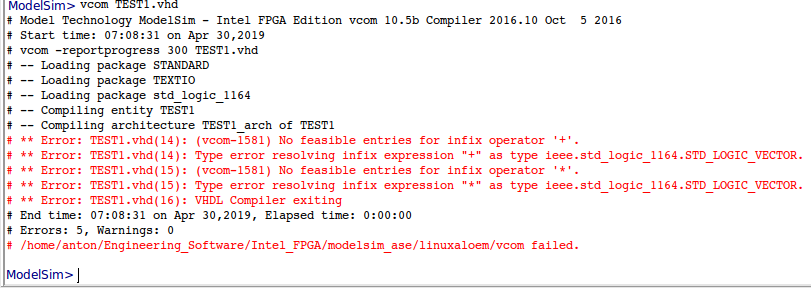

assume we have alogic system that need to performe few arithmetic operations, and also assume that this system need to be descride with std_logic data type, doing regular compilation will not work directly, obviesly synthesis will fail as well.

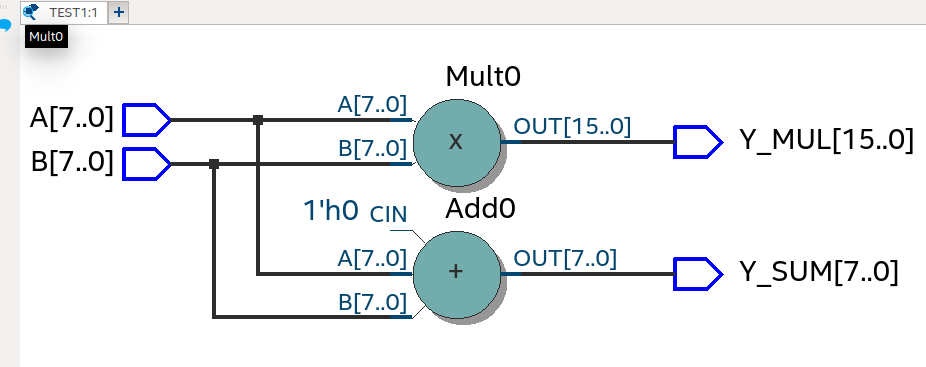

Lets observe this logic system that have 2 8-bit inputs and have 2 outputs one for sum and one for multiplay, if we use regular std_logic_vector (or bit_vector) it will not pass even compilation, also note that for the MUL we need higher range of result is higher then the lenght of the inputs.

There is a package under IEEE library that used to enhance the std_logic_vector and can provide arithmetic operations on signed or\and unsigned numbers, we will discusss and use for now only unsigned package, when we meet appropriate example where sign package is need we will use it.

Notes

1. there is 2 packages that we can use the std_logic_signed and std_logic_unsigned.

2. VHDL-2008 have numeric_std_unsigned which have more features.

3. you allowed to use only one package of unsigned or singed when use it.

4. when using compare (like <, > etc) the std_logic_unsigned help with problematic cases when comparing inputs that have different size\lenght (will be discussed seperatly).

5. for '+' it possible to add std_logic_vector and std_logic.

to make a package visiable add: use ieee.std_logic_unsigned.all; before the entity declartion but after the library ieee;.

as Good Practice we will use the declaration if IEEE package always when writing systems by default, unless there is spesific cases when exclusivly would to use other types. in addition almost all projects examples and complex systems will be written using IEEE std_logic.

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

Compile fail - VHDL not know what is '+' or '-'

Compile pass - when make std_logic_unsigned included

after using the std_logic_unsigned package the compilation is passing.

note that std_logic_unsigned package indeed loaded to simulator.

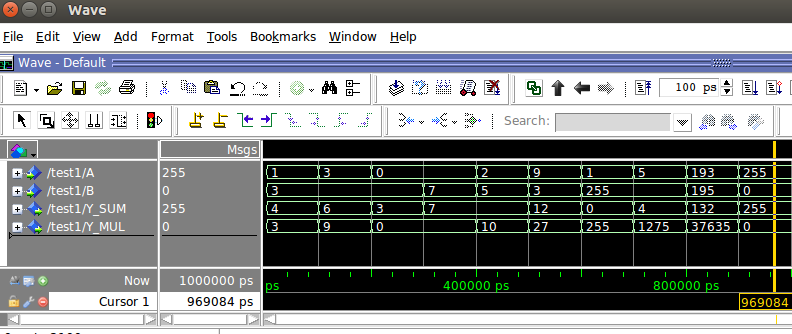

we using TCL script that will test several cases, include cases where one input is Zero, we can see that the system behave correctly and perform multiplay and add operations.

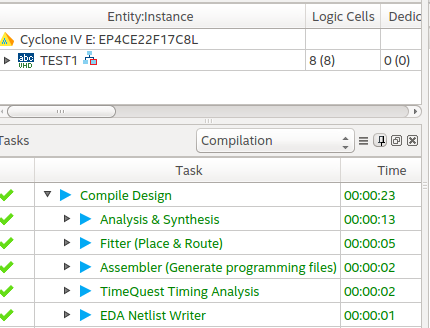

the usage of arithmetic package is synthesisable and can be used widely in writing H\W for synthesis.

passing all the synthesis process on EP4CE22F17C8L