Package is an Basic Compilation unit - it possible to compile Package on its own

it mean that we can compile package seperatly from VHDL system aka we dont need entity first, also note that we can use package with several entitys.

package can have

1. package declaration - see example in right, it used for declaration on constants and functions from left you can see an example of simple package

2. package body - used for functions and procedure (include internal functions) implementaion, this is optional part as it not mandatory to use it.

package can be compiled sepereratly from entity and\or architecture, note that when you use the package in entity it must be compiled before

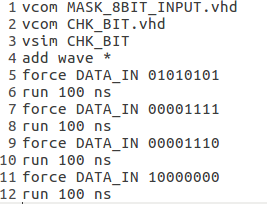

1. it must be compiled first

2. we need to include it before the entity - the most commen way is by using use work.package_name.all.

3. we can include every constant one by one like this

4. another to use package is like this

average developer will preffer use this work.package_name.all.

this is because it will make all the elements in package be visible

note that we compilled the package first and only then we compiled the vhd file with the entity that use it.

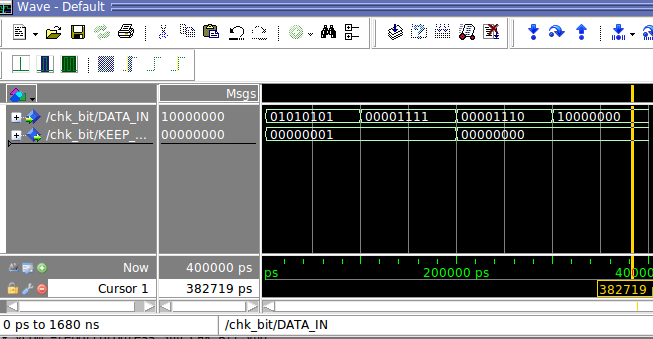

below are behaive of your system, we just masking everything bit first bit of the input signal.