VHDL provide multiple types of numeric data types, in general VHDL designed for simulation of logic systems so obvies that not all of the datatypes are be able to be synthesized, in general Synthesis S\W need to transfer the data types to wires, for example asuume we have an input port of integer data type and it constrained (limited) to be from 0 to 15 Synthesis S\W may represent it as 4 bit binary line. we will discuess during this architecle in deep.

VHDL data types for numbers

1) integer data types - contain signed and unsigned integers from -2^31 to 2^31 - 1.

2) real data types - contain the floating point data type.

Notes

a. VHDL not allow automatic cast (it strongly typed HDL) there force it illigal to assign integer value in to real port\signal.

b. integer data type have 2 subtypes natural that contain all numbers 0,1,2.... and positive whitch exclude the zero (1,2,3...)

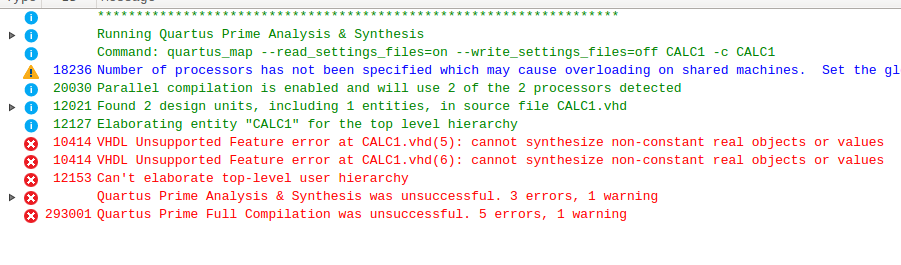

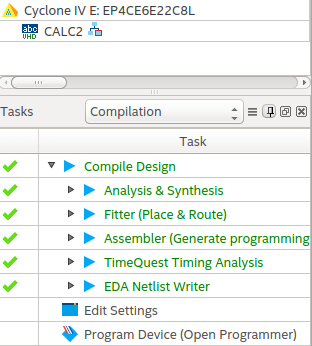

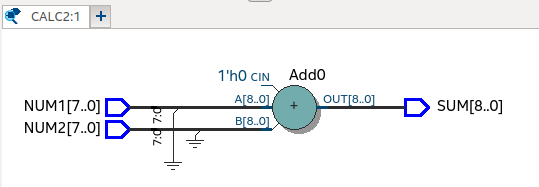

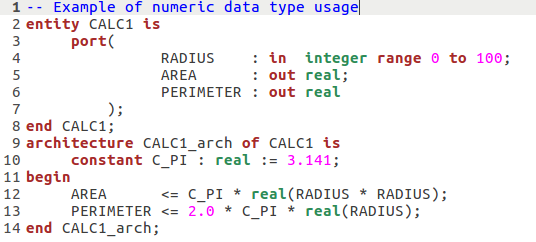

as mention synthesis will be discussed seperatly and the example from right is NOT synthesizable as real is not supported (tested with Quartos 17.1)

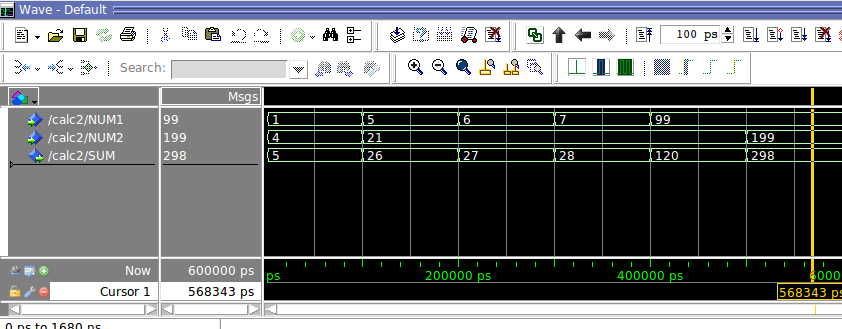

Note that we casted the RADIUS by read(RADIUS) also we can cast the whole expression, in addition note that when calculating and assign to real datatype we cannot use discreat integer numbers directly but we used then as real (2.0 instead of 2).

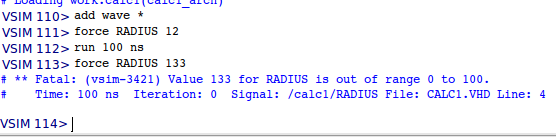

The integer data type is constrained and limited from 0 to 100.

1.we used force\run commands to execute simulation

2. observe the waive form for MISC integer data type.

Notice about simulation

we cannot use values that exceed what we constained, the modelsimm tool will not let us to continue simulations.