writted in VHDL compiled with Modelsim example of 1 bit full adder using logic gates

1. used and,or,xor logic gates to represent the system

2. if the input is from same type we can use logic operations multiple times, like a xor b xor c xor b...

3. when logic operation is different need to use brackets, fail to do it will cause problems for example a xor b and c is illigal, but you will need to use this form: (a xor b) and c it also better for readability.

4. as menthion previesly that commands in architecture are existing in concurrent (both happen in same time), and thier order is not important.

Full Adder is a device that adds 2 bits and also the carry in, it preduce sum with carry-out. it a very usefull device as it can be easily duplicated making it generic device to adding larger numberes. (we will discuss later technics of duplicating and using it as component).

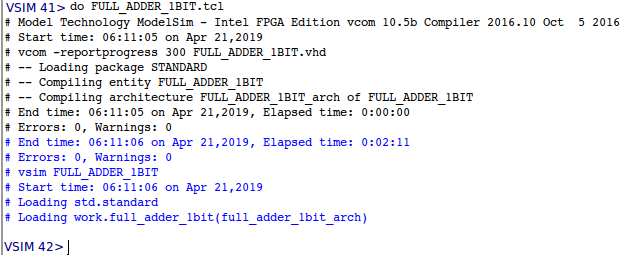

1. open modelsim and ensure you are in the directory where your VHD file is

2. we will use modelsim TCL based script for compilation and simulation process.

3. note that we change the carry in only twice, only when we scan all the permutations of previus state of the carry in.

we used modelsim script for simulation process, we can see that it compilled and loaded to simulator the full adder entity and run simulation by executing force and run commands.

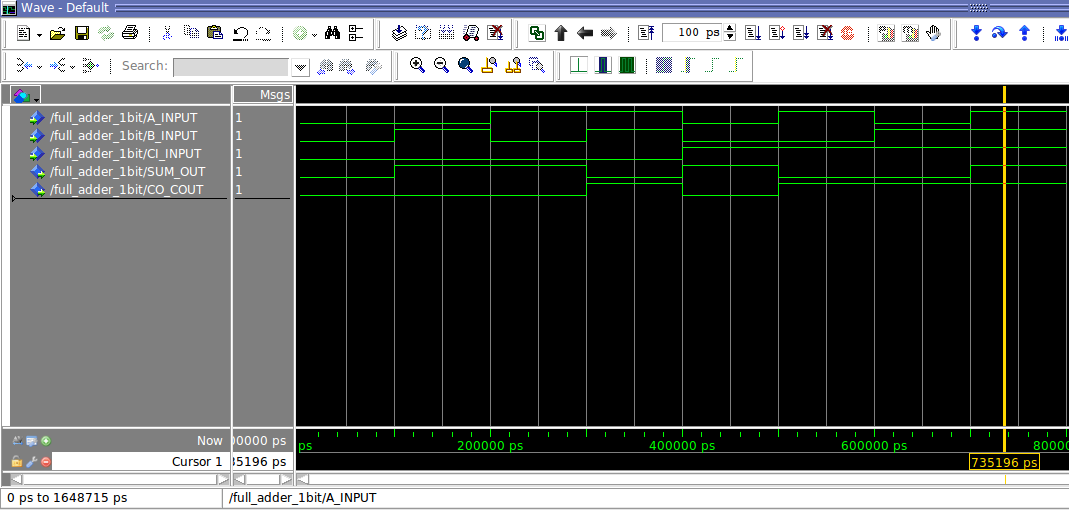

you can identify that below are waveform work as Full adder, note that only when carry-in is '1' and both inputs are '1' the both carry-out and sum outputs are '1'.