Generic Sizes\Devices

VHDL allow to use generic size Element and\or elemetns that can be custumized by user.

using generic statment we can create parametrized inputs\outputs that can be defined in during the component

usage and it also have default value.

|

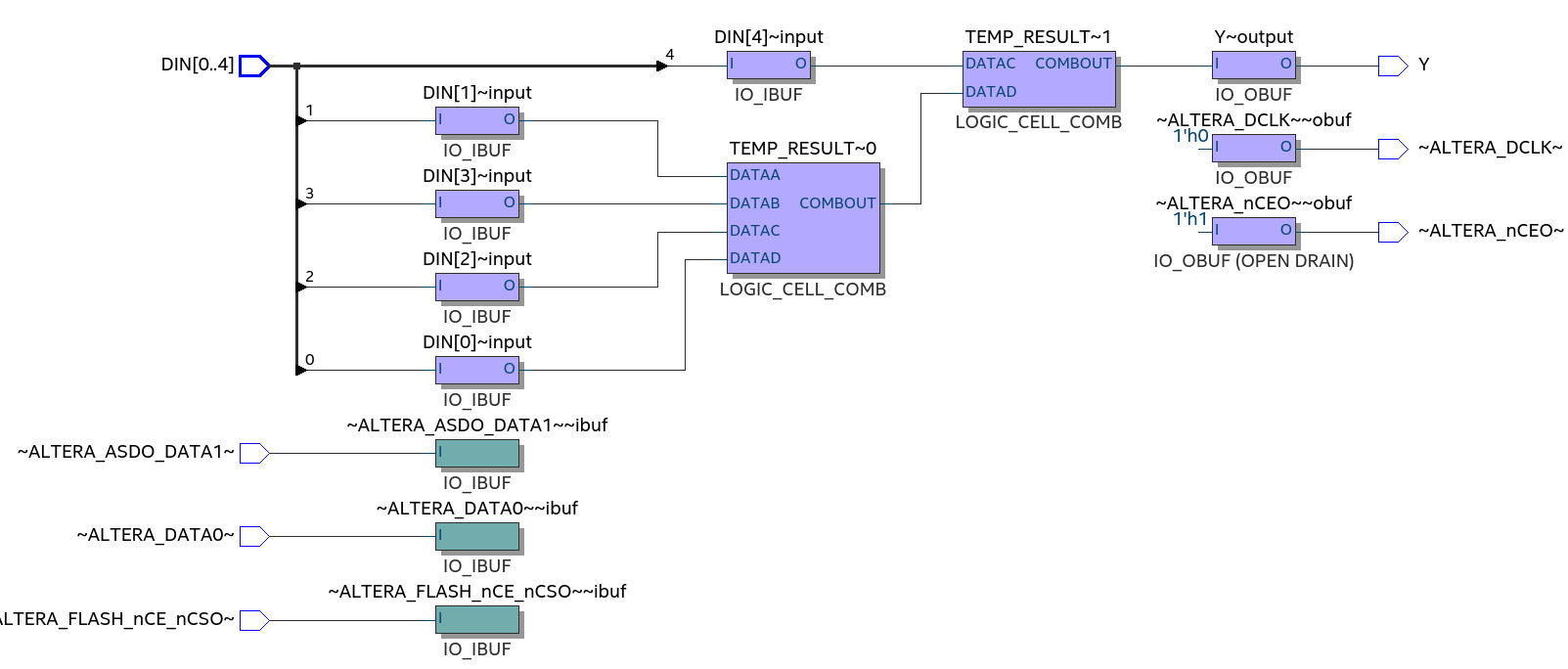

Example of the AND with 5 inputs

|

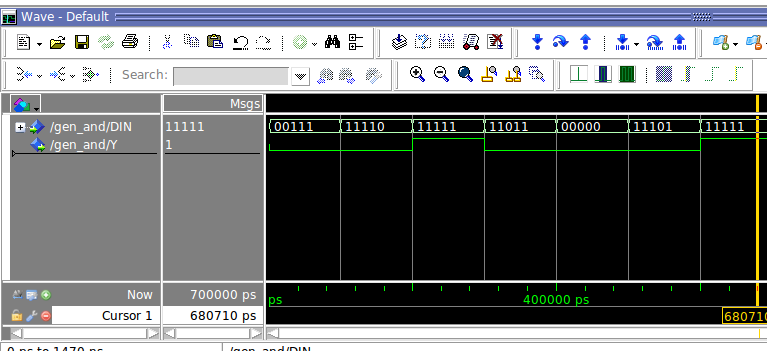

Waveform of AND with 5 inputs

we used simple modelsim commands as example is very simple

|

Waveform of AND with 5 inputs

|

Using Flexible AND Gate as componenet

the main purpose of generic statment is to make a component generic (or "flexible"),

this improve VHDL capability by making the launguage much stronger.

Note - there is credefined packages that have generic devices for general usage like LPM package.

in this example we

1. declated GEN_AND as component in the declarative part of the arhictecture

2. used it 3 times - it mandory to use label when calling a component.

3. we used the generic map key to setup the new size of every component.

4. when using generic map before the part map we dont use ";"

|

Example of 3 different AND gates by using flexible and

|

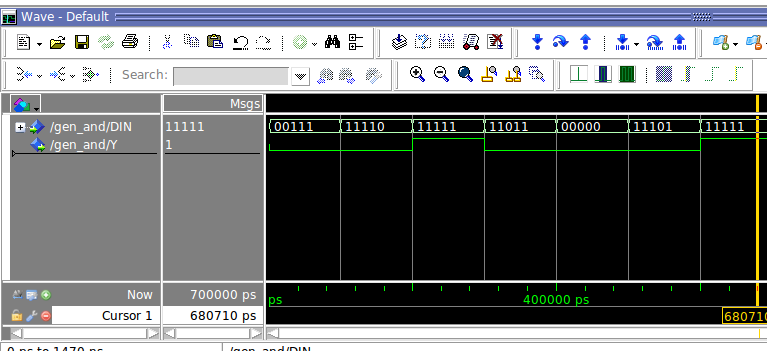

Waveform of 3 different AND gates

we use one 15 bit input and used slices of it to useas imput for the GEN_AND gates.

we used TCL script to run simulation

vcom GEN_AND.vhd

vcom MISC_ANDS.vhd

vsim MISC_ANDS

add wave *

force INPUT 000111101111111

run 100 ns

force INPUT 111000011111111

run 100 ns

force INPUT 011000011111110

run 100 ns

force INPUT 111000100000001

run 100 ns

force INPUT 111111111111111

run 100 ns

|

Waveform of AND with 5 inputs

|

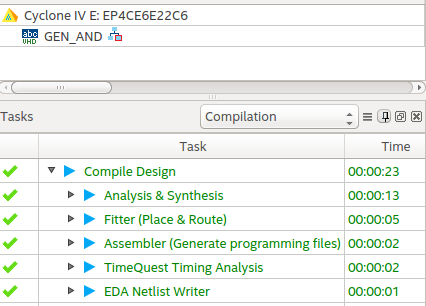

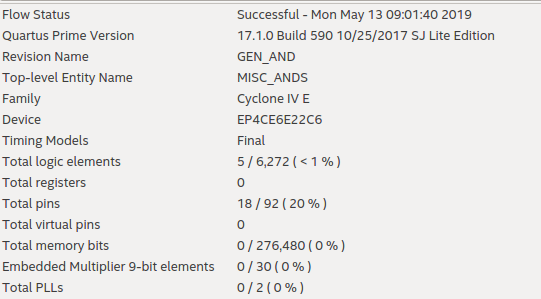

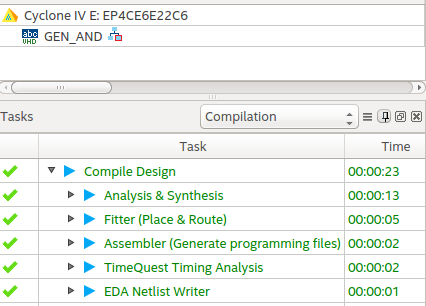

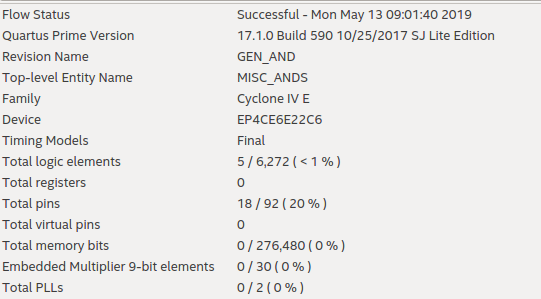

Synthesis of GEN_AND Gate

we will use EP4CE6E22C6 Cyclone 4 FPGA to for synthesis of GEN_AND gate

also observe that we used only 2 logic elements from the Device.

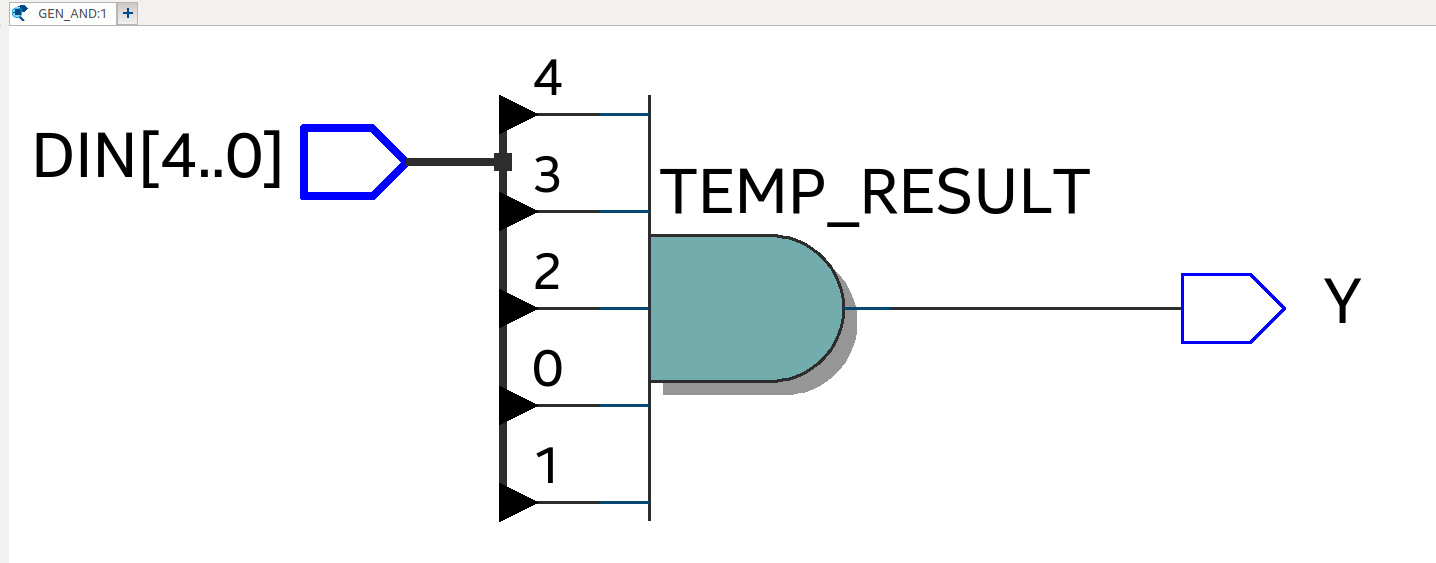

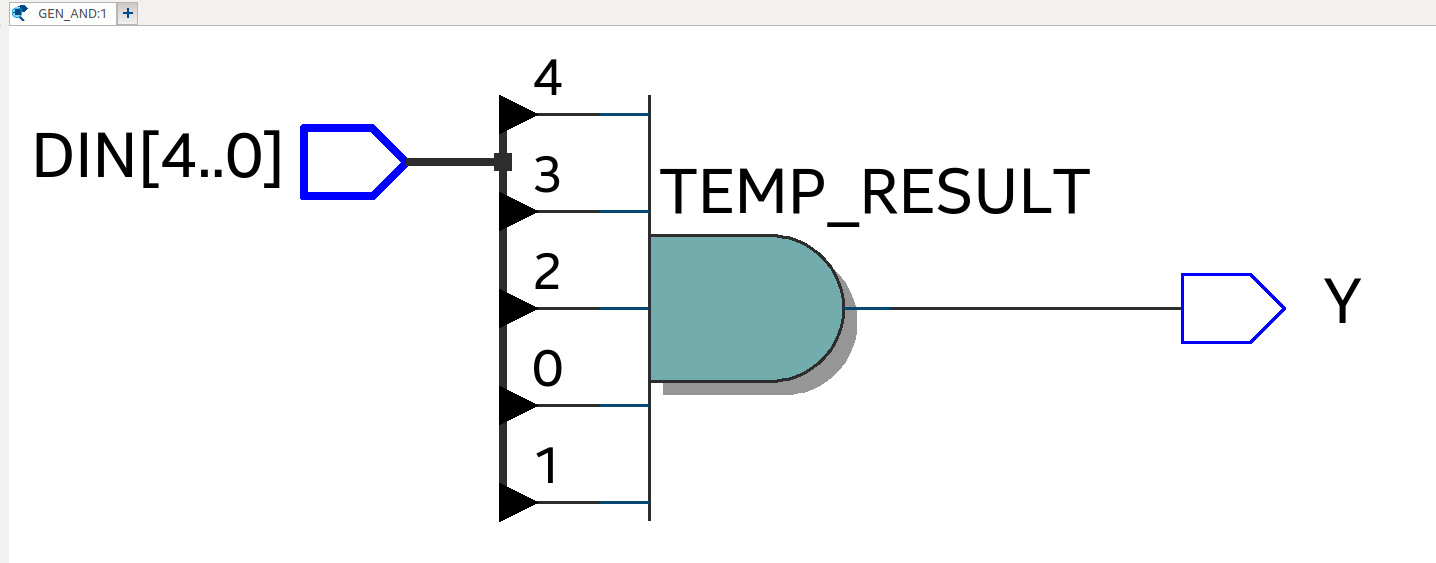

in RTL we can see that whatever defined as default value of generic statment is what Synthesis tool (Quartos) decide to

generate, we can see that we used 2 LOGIC_CELL_COMB as each of them can create upto 4 gate AND and the input have 5 then we used 2

of the LOGIC_CELL_COMB to synthsize the logic.

|

Example of RTL view

Below are the way how Quartos arrange LUTs

|

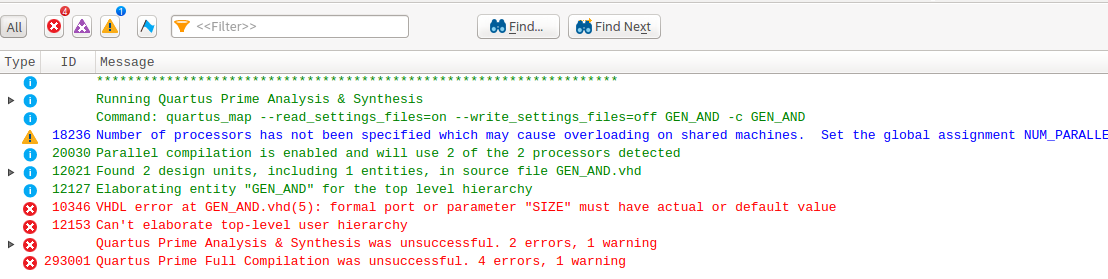

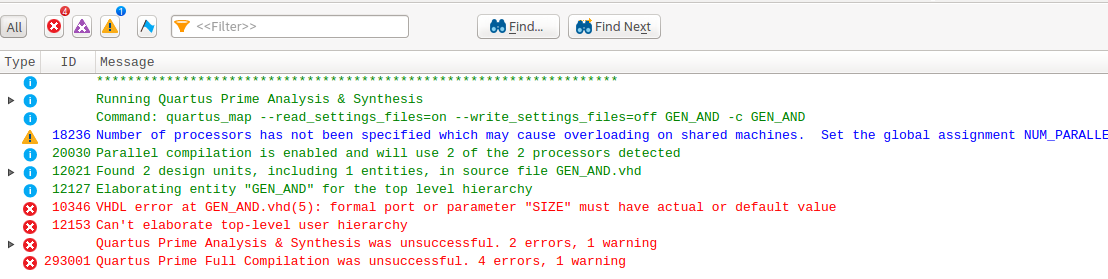

Generic values for synthesis must be constrained

of we decide to remove the default assignment in the generic statment.

then Quartos will not be able to sinthesis it, as Quartos done know what lenght of the AND gate you will need.

when using generics in synthesis need to have either

● generic with default value in the VHDL file of the component.

● when using component with generic value define it in the generic map

|

Quartos fail because GEN_AND not default size not defined.

|

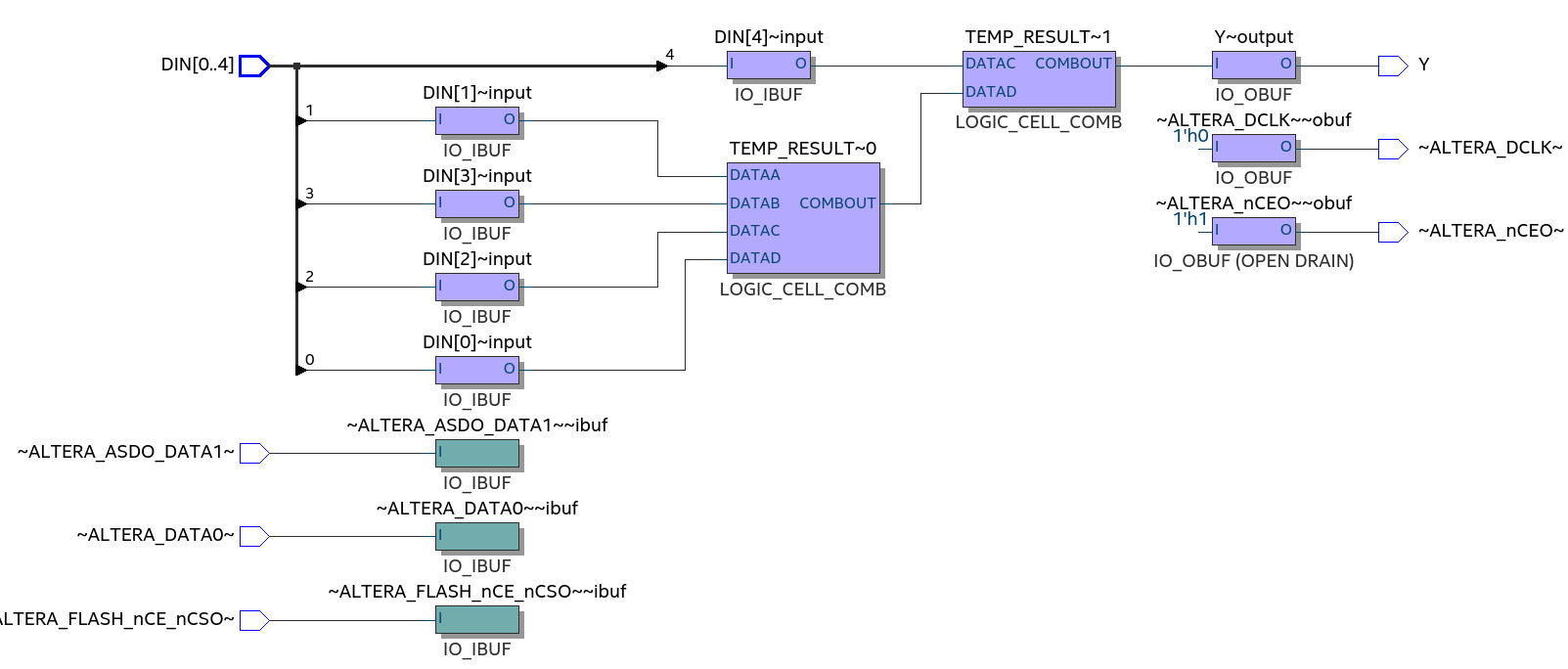

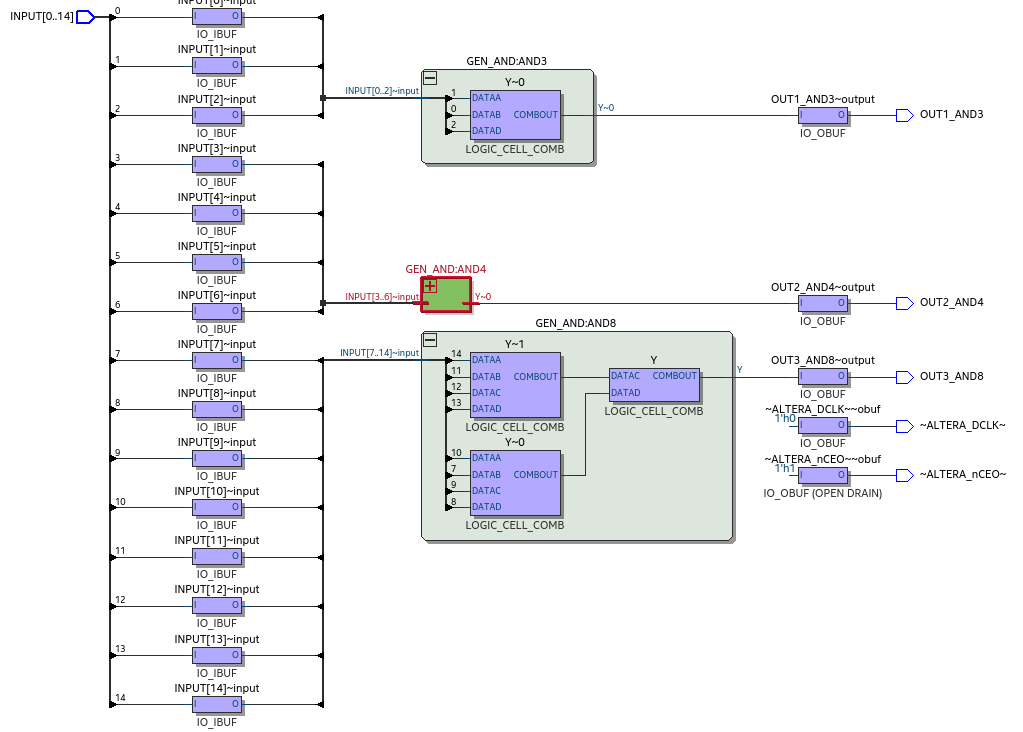

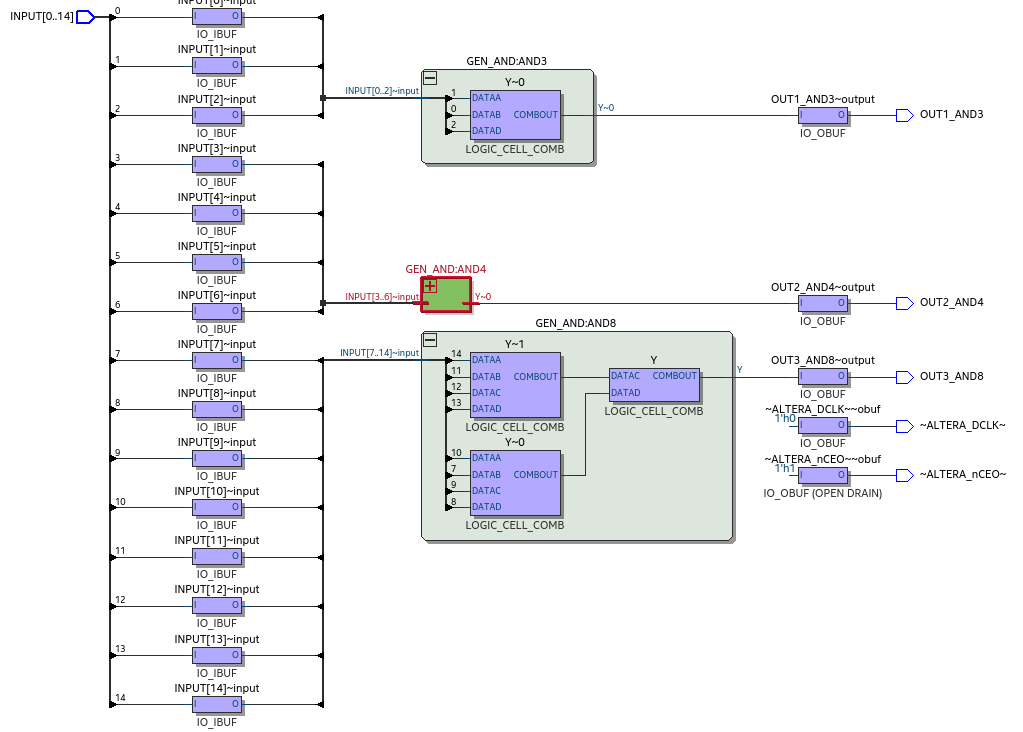

Example when synthesize a logic that use constrained components

the synthesis of MISC_ANDS will work as during instantiation of the component in the generic map we used

Note

need to set MISC_ANDS as top-level entity in quartos before try to synthesize it.

obviesly will be used more LOGIC_CELLs

|

Example of RTL of MISC_ANDS

Example of RTL of MISC_ANDS

|