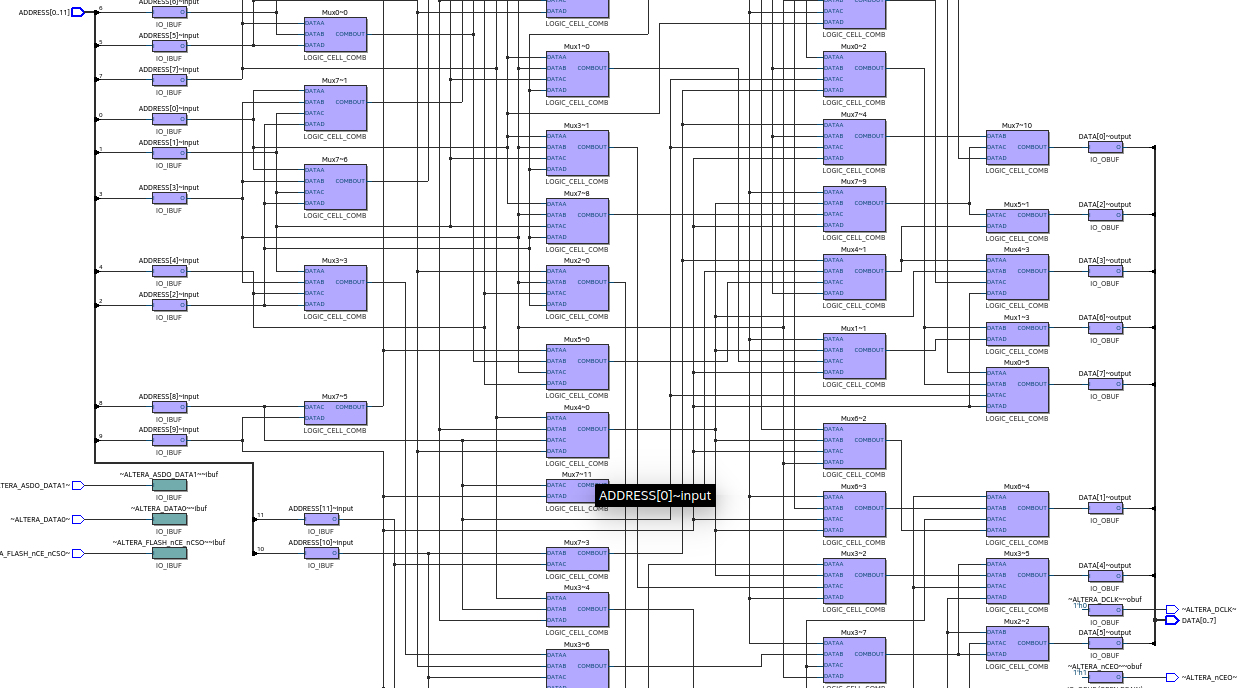

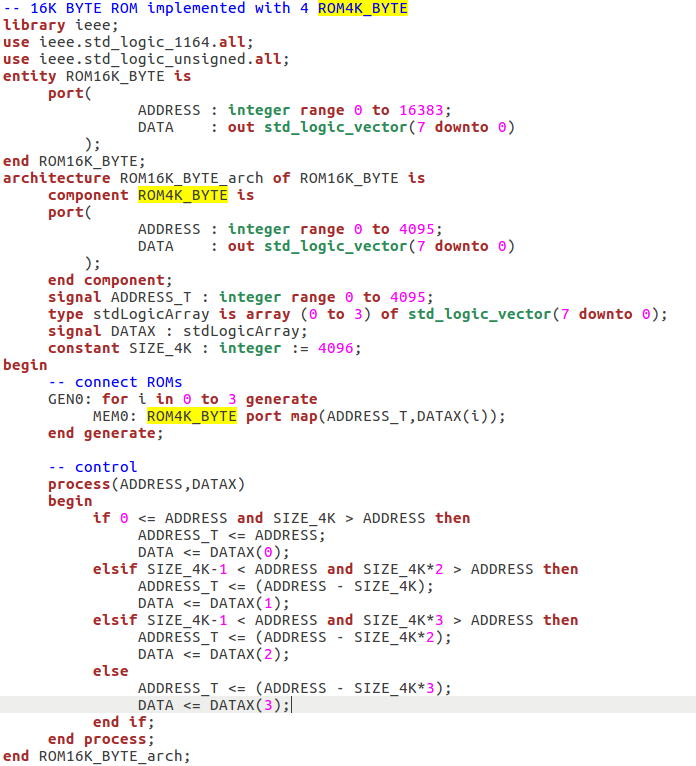

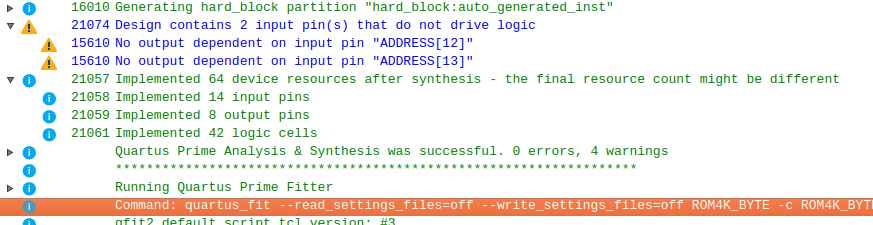

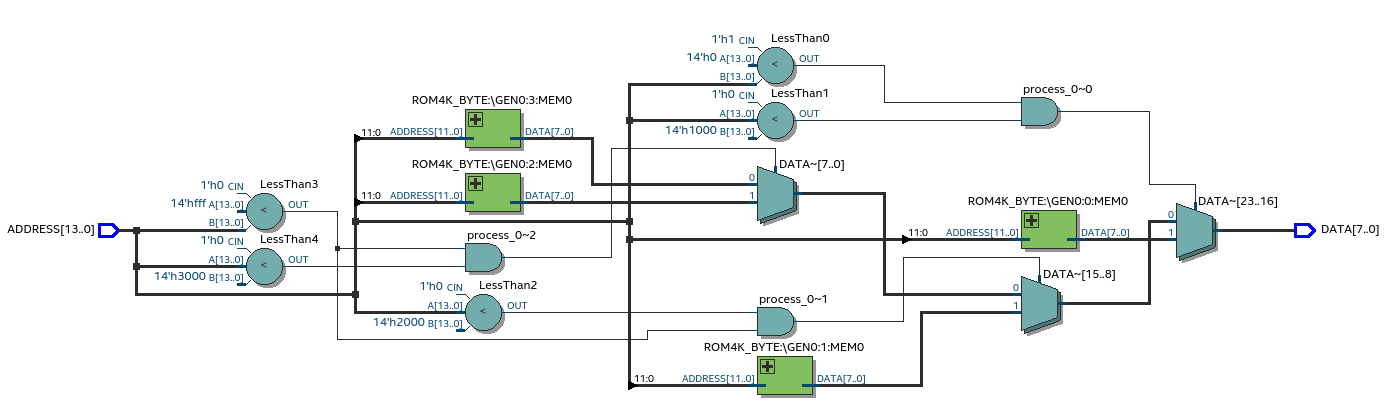

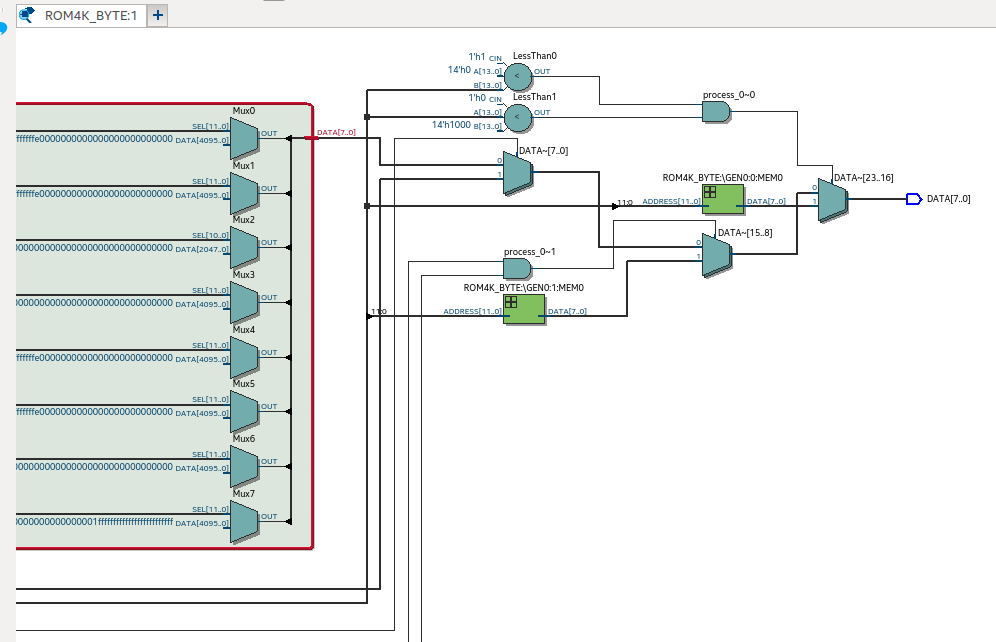

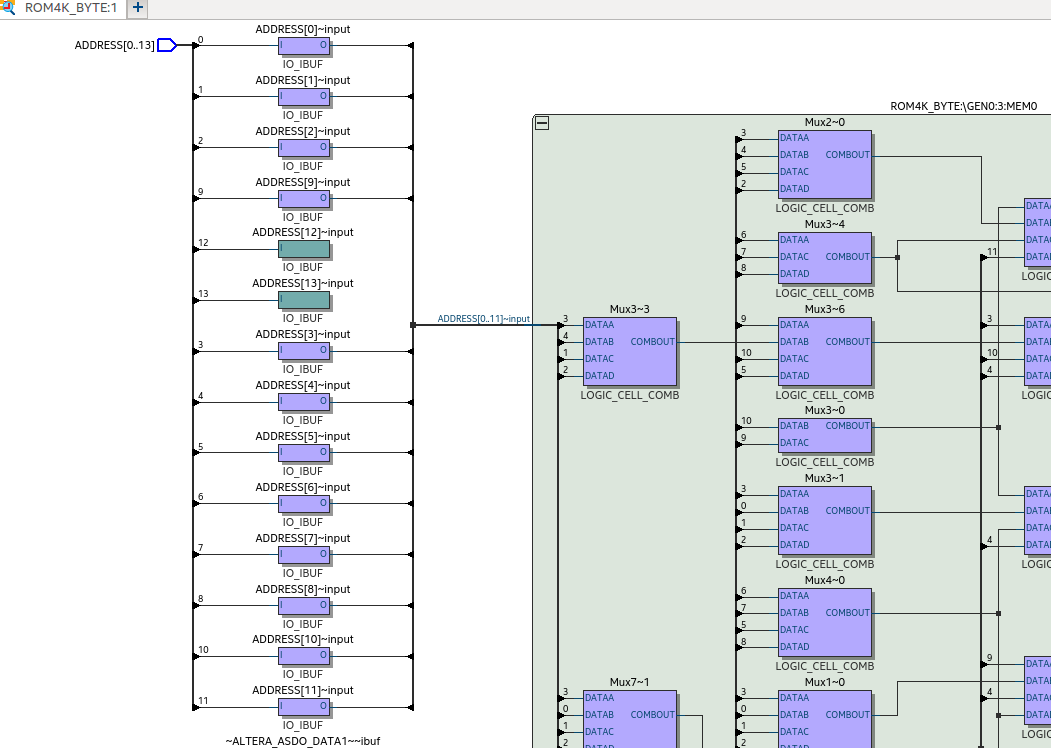

ROMs can be done with larger arrays, and can be initizlized in seperate ways. in the below example we have ROM of 4K BYTE size , it wide is 1 BYTE (8 bits) and it lenght is 4K (it have 4K address). we will use positional assignemt in the constant of the array size

ways to assign values

● num1(address) to num2(address) - assign same values to range of address

● num1(address) | num2(address) - assign same values to list of address (like or)

● num1(address) - assign one value to one address

● others => (values) - assign default value to rest of th e address

The ROM itself is very basic and simple and we we can simulate it from modelsim console directly.