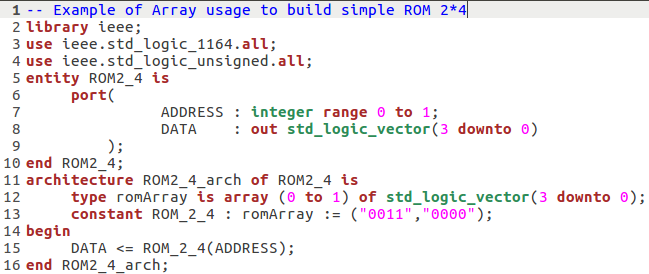

we can define arrays from multiple data types, need to notice that

bit_vector\std_logic_vector are arrays from bit\std_logic.

array in VHDL can be constrained and un-constrained

Example1: type myArrayOfBits is array (0 to 7) of bit;

Example2: type std_logic_vector is array (natural range <> of std_logic;

The second example is from standard std_logic_1164 package.

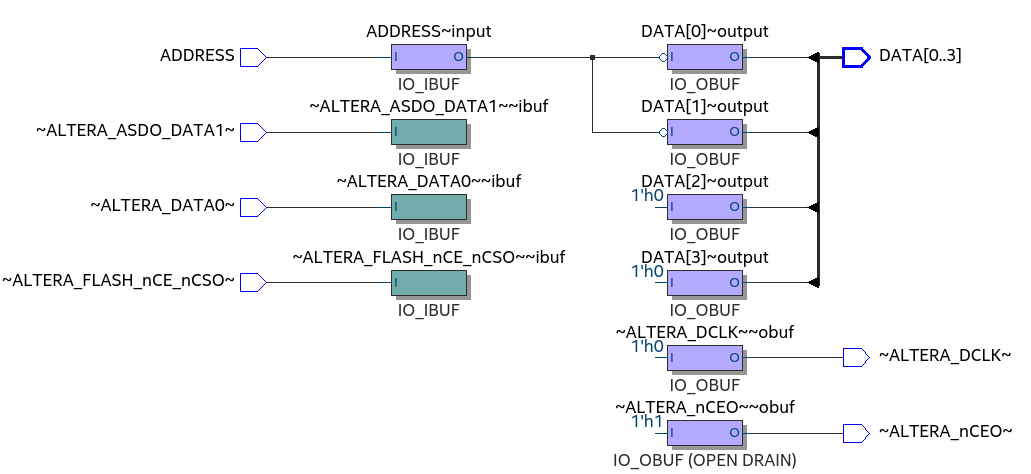

Example of Simple ROM 2 x 4

in this SImple Example we will a have a simple ROM memory that have 2 adress and 4 bit wide of memory, we used the address as ineteger as VHDL does not translate index (integer) to std_logic, when we cover functions we will solve this more elegantly, however the integer data type fully supported by synthesis S\W.

The ROM itself is very basic and simple and we we can simulate it from modelsim console directly.